**LS7366R**

LSI Computer Systems, Inc. 1235 Walt Whitman Road, Melville, NY 11747 (631) 271-0400 FAX (631) 271-0405

# 32-BIT QUADRATURE COUNTER WITH SERIAL INTERFACE

# **GENERAL FEATURES:**

- Operating voltage: 3V to 5.5V (VDD VSS)

- 5V count frequency: 40MHz

- 3V count frequency: 20MHz

- 32-bit counter (CNTR).

- 32-bit data register (DTR) and comparator.

- 32-bit output register (OTR).

- Two 8-bit mode registers (MDR0, MDR1) for programmable functional modes.

- 8-bit instruction register (IR).

- 8-bit status register (STR).

- Latched Interrupt output on Carry or Borrow or Compare or Index.

- Index driven counter load, output register load or counter reset.

- Internal quadrature clock decoder and filter.

- x1, x2 or x4 mode of quadrature counting.

- Non-quadrature up/down counting.

- Modulo-N, Non-recycle, Range-limit or Free-running modes of counting

- 8-bit, 16-bit, 24-bit and 32-bit programmable configuration synchronous (SPI) serial interface

- LS7366R (DIP), LS7366R-S (SOIC), LS7366R-TS (TSSOP)

- See Figure 1 -

### **SPI/MICROWIRE** (Serial Peripheral Interface):

- Standard 4-wire connection: MOSI, MISO, SS/ and SCK.

- Slave mode only.

#### **GENERAL DESCRIPTION:**

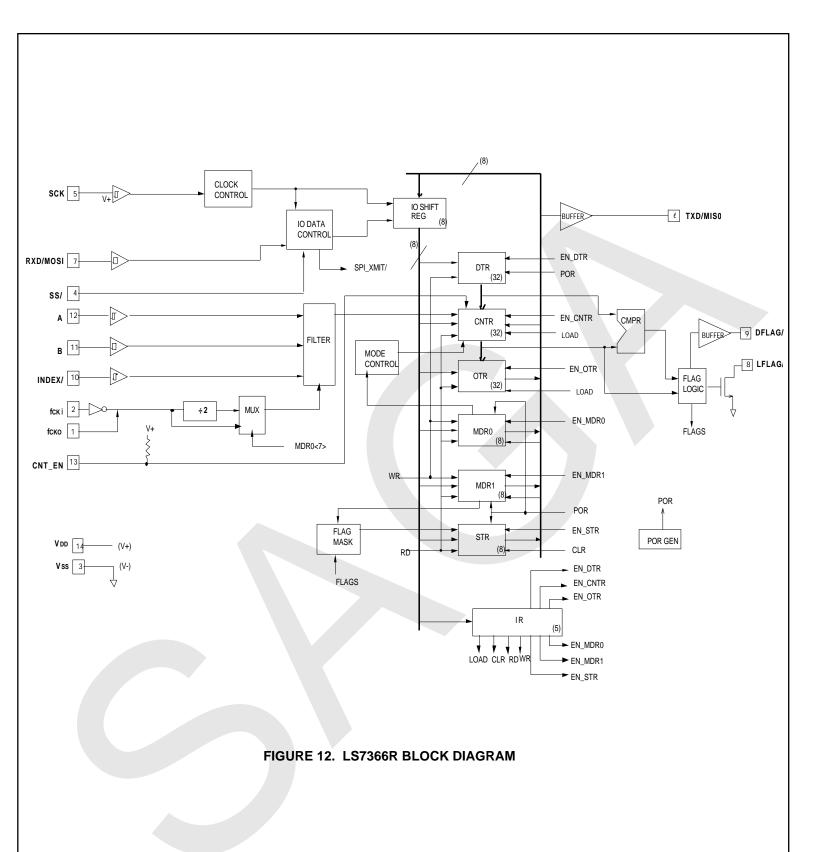

LS7366R is a 32-bit CMOS counter, with direct interface for quadrature clocks from incremental encoders. It also interfaces with the index signals from incremental encoders to perform variety of marker functions.

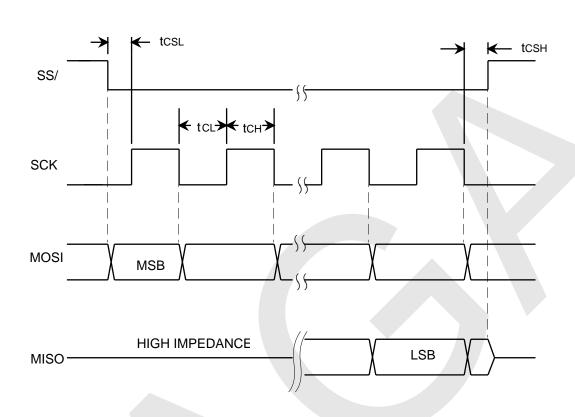

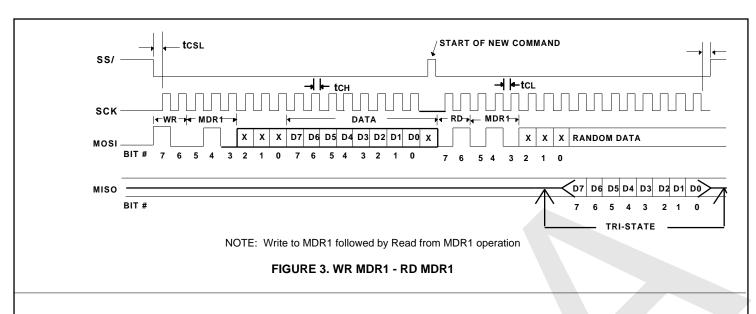

For communications with microprocessors or microcontrollers, it provides a 4-wire SPI/MICROWIRE bus. The four standard bus I/Os are SS/, SCK, MISO and MOSI. The data transfer between a microcontroller and a slave LS7366R is synchronous. The synchronization is done by the SCK clocks supplied by the microcontroller. Each transmission is organized in blocks of 1 to 5 bytes of data. A transmission cycle is intitiated by a high to low transition of the SS/ input. The first byte received in a transmission cycle is always an instruction byte, whereas the second through the fifth bytes are always interpreted as data bytes. A transmission cycle is terminated with the low to high transition of the SS/ input. Received bytes are shifted in at the MOSI input, MSB first, with the leading edges (high transition) of the SCK clocks. Output data are shifted out on the MISO output, MSB first, with the trailing edges (low transition) of the SCK clocks.

May 2006 PIN ASSIGNMENT TOP VIEW S 14 **V** DD fско 13 CNT\_EN fcki SS 11 B 10 INDEX/ SCK MISO 9 DFLAG/ 8 LFLAG/ MOSI FIGURE 1

Read and write commands cannot be combined. For example, when the device is shifting out read data on MISO output, it ignores the MOSI input, even though the SS/ input is active. SS/ must be terminated and reasserted before the device will accept a new command.

The counter can be configured to operate as 1, 2, 3 or 4-byte counter. When configured as an n-byte counter, the CNTR, DTR and OTR are all configured as n-byte registers, where n = 1, 2, 3 or 4. The content of the instruction/data identity is automatically adjusted to match the n-byte configuration. For example, if the counter is configured as a 2-byte counter, the instruction "write to DTR" expects 2 data bytes following the instruction byte. If the counter is configured as a 3-byte counter, the same instruction will expect 3 bytes of data following the instruction byte.

Following the transfer of the appropriate number of bytes any further attempt of data transfer is ignored until a new instruction cycle is started by switching the SS/ input to high and then low.

The counter can be programmed to operate in a number of different modes, with the operating characteristics being written into the two mode registers MDR0 and MDR1. Hardware I/Os are provided for event driven operations, such as processor interrupt and index related functions.

#### I/O Pins:

Following is a description of all the input/output pins.

#### **A** (Pin 12) **B** (Pin 11)

Inputs. A and B quadrature clock outputs from incremental encoders are directly applied to the A and B inputs of the LS7366R. These clocks are ideally 90 degrees out-of-phase signals. A and B inputs are validated by on-chip digital filters and then decoded for up/down direction and count clocks. In non-quadrature mode, A serves as the count input and B serves as the direction input (B = high enables up count, B = low enables down count). In non-quadrature mode, the A and B inputs are not filtered internally, and are instantaneous in nature.

#### INDEX/ (Pin 10)

Input. The INDEX/ is a programmable input that can be driven directly by the Index output of an incremental encoder. It can be programmed via the MDR0 to function as one of the following:

LCNTR (load CNTR with data from DTR), RCNTR (reset CNTR), or LOTR (load OTR with data from CNTR). Alternatively, the INDEX input can be masked out for "no functionality".

In quadrature mode, the INDEX/ input can be configured to operate in either synchronous or asynchronous mode. In the synchronous mode the INDEX/ input is sampled with the same filter clock used for sampling the A and the B inputs and must satisfy the phase relationship in which the INDEX/ is in the active level of Logic 0 during a minimum of a quarter cycle of both A and B High or both A and B Low. In non-quadrature mode, the INDEX/ input is unconditionally set to the asynchronous mode. In the asynchronous mode, the INDEX/ input is not sampled and can be applied in any phase relationship with respect to A and B.

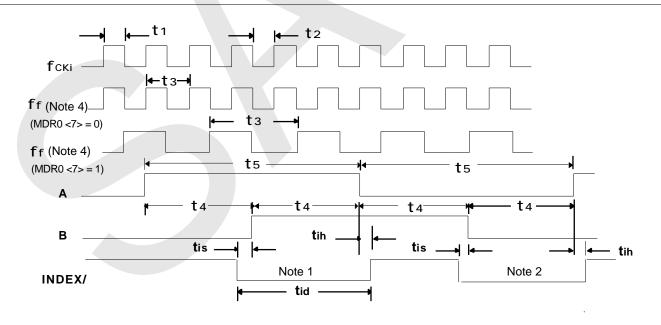

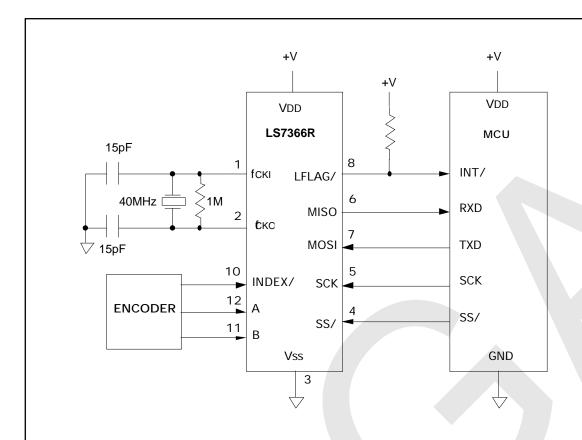

# fcкі (Pin 2), fcко (Pin 1)

Input, Output. A crystal connected between these 2 pins generates the basic clock for filtering the A, B and INDEX/inputs in the quadrature count mode. Instead of a crystal the fcki input may also be driven by an external clock.

The frequency at the fc $\kappa$ i input is either divided by 2 (if MDR0 <B7> = 1) or divided by 1 (if MDR0 <B7> = 0) for the filter circuit. For proper filtering of the A, B and the Index/inputs the following condition must be satisfied:

#### ff 4fQA

Where fr is the internal filter clock frequency derived from the fcki in accordance with the status of MDR0 <B7> and fQA is the maximum frequency of Clock A in quadrature mode. In non-quadrature count mode, fcki is not used and should be tied off to any stable logic state.

#### **SS/** (Pin 4)

A high to low transition at the SS/ (Slave Select) input selects the LS7366R for serial bi-directional data transfer; a low to high transition disables serial data transfer and brings the MISO output to high impedance state. This allows for the accommodation of multiple slave units on the serial I/O.

#### **CNT\_EN** (Pin 13)

Input. Counting is enabled when CNT\_EN input is high; counting is disabled when this input is low. There is an internal pull-up resistor on this input.

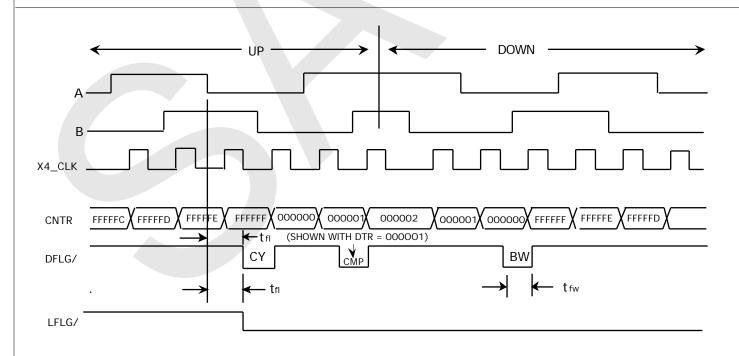

#### LFLAG/ (Pin 8), DFLAG/ (Pin 9)

Outputs. LFLAG/ and DFLAG/ are programmable outputs to flag the occurences of Carry (counter overflow), Borrow (counter underflow), Compare (CNTR = DTR) and INDEX. The LFLAG/ is an open drain latched output. In contrast, the DFLAG/ is a pushpull instantaneous output. The LFLAG/ can be wired in multislave configuration, forming a single processor interrupt line. When active LFLAG/ switches to logic 0 and can be restored to the high impedence state only by clearing the status register, STR. In contrast, the DFLAG/ dynamically switches low with occurences of Carry, Barrow, Compare and INDEX conditions.

The configuration of LFLAG/ and DFLAG/ are made through the control register MDR1.

#### MOSI (RXD) (Pin 7)

Input. Serial output data from the host processor is shifted into the LS7366R at this input.

#### MISO (TXD) (Pin 6)

Output. Serial output data from the LS7366R is shifted out on the MISO (Master In Slave Out) pin. The MISO output goes into high impedance state when SS/ input is at logic high, providing multiple slave-unit serial outputs to be wire-ORed.

#### SCK (Pin 5)

Input. The SCK input serves as the shift clock input for transmitting data in and out of LS7366R on the MOSI and the MISO pins, respectively. Since the LS7366R can operate only in the slave mode, the SCK signal is provided by the host processor as a means for synchronizing the serial transmission between itself and the slave LS7366R.

#### **REGISTERS:**

The following is a list of LS7366 internal registers:

Upon power-up the registers DTR, CNTR, STR, MDR0 and MDR1 are reset to zero.

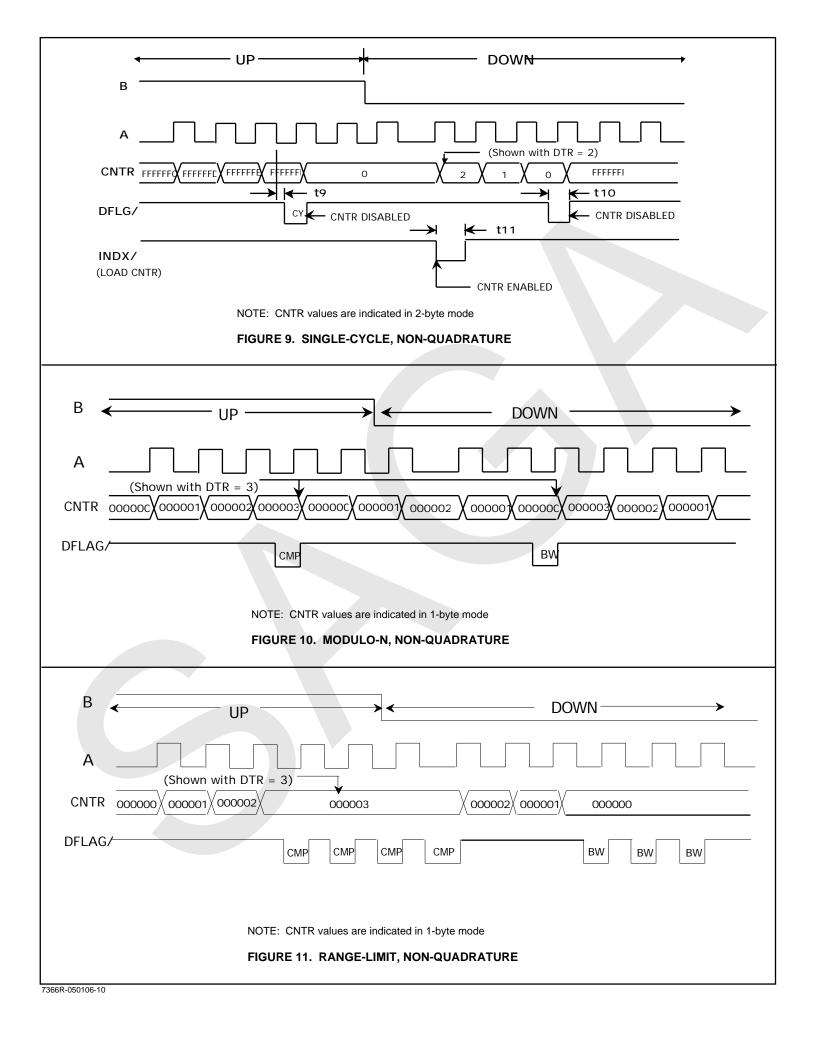

**DTR.** The DTR is a software configurable 8, 16, 24 or 32-bit input data register which can be written into directly from MOSI, the serial input. The DTR data can be transferred into the 32-bit counter (CNTR) under program control or by hardware index signal. The DTR can be cleared to zero by software control. In certain count modes, such as modulo-n and range-limit, DTR holds the data for "n" and the count range, respectively. In compare operations, whereby compare flag is set, the DTR is compared with the CNTR.

CNTR. The CNTR is a software configurable 8, 16, 24 or 32-bit up/down counter which counts the up/down pulses resulting from the quadrature clocks applied at the A and B inputs, or alternatively, in non-quadrature mode, pulses applied at the A input. By means of IR intructions the CNTR can be cleared, loaded from the DTR or in turn, can be transferred into the OTR.

OTR. The OTR is a software configuration 8, 16, 24 or 32-bit register which can be read back on the MISO output. Since instantaneous CNTR value is often needed to be read while the CNTR continues to count, the OTR serves as a convenient dump site for instantaneous CNTR data which can then be read without interfering with the counting process.

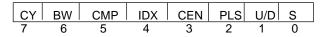

STR. The STR is an 8-bit status register which stores count related status information.

CY: Carry (CNTR overflow) latch

BW: Borrow (CNTR underflow) latch CMP: Compare (CNTR = DTR) latch

IDX: Index latch

CEN: Count enable status: 0: counting disabled,

1: counting enabled

PLS: Power loss indicator latch; set upon power up

U/D: Count direction indicator: 0: count down, 1: count up

S: Sign bit. 1: negative, 0: positive

IR. The IR is an 8-bit register that fetches instruction bytes from the received data stream and executes them to perform such functions as setting up the operating mode for the chip (load the MDR) and data transfer among the various registers.

> B7 B6 B5 B4 B3 B2 В1 B0

B2 B1 B0 = XXX (Don't care)

B5 B4 B3 = 000: Select none

= 001: Select MDR0

= 010: Select MDR1

= 011: Select DTR

= 100: Select CNTR = 101: Select OTR

= 110: Select STR

= 111: Select none

B7 B6 = 00: CLR register = 01: RD register

= 10: WR register

= 11: LOAD register

The actions of the four functions, CLR, RD, WR and LOAD are elaborated in Table 1.

| TABLE 1         |         |          |                                                |  |  |  |

|-----------------|---------|----------|------------------------------------------------|--|--|--|

| Number of Bytes | OP Code | Register | Operation                                      |  |  |  |

|                 |         | MDR0     | Clear MDR0 to zero                             |  |  |  |

|                 |         | MRD1     | Clear MDR1 to zero                             |  |  |  |

| 1               | CLR     | DTR      | None                                           |  |  |  |

|                 |         | CNTR     | Clear CNTR to zero                             |  |  |  |

|                 |         | OTR      | None                                           |  |  |  |

|                 |         | STR      | Clear STR to zero                              |  |  |  |

|                 |         | MDR0     | Output MDR0 serially on TXD (MISO)             |  |  |  |

|                 |         | MDR1     | Output MDR1 serially on TXD (MISO)             |  |  |  |

| 2 to 5          | RD      | DTR      | None                                           |  |  |  |

|                 |         | CNTR     | Transfer CNTR to OTR, then output OTR serially |  |  |  |

|                 |         |          | on TXD (MISO)                                  |  |  |  |

|                 |         | OTR      | Output OTR serially on TXD (MISO)              |  |  |  |

|                 |         | STR      | Output STR serially on TXD (MISO)              |  |  |  |

|                 |         | MDR0     | Write serial data at RXD (MOSI) into MDR0      |  |  |  |

|                 | 14/5    | MDR1     | Write serial data at RXD (MOSI) into MDR1      |  |  |  |

| 2 to 5          | WR      | DTR      | Write serial data at RXD (MOSI) into DTR       |  |  |  |

|                 |         | CNTR     | None                                           |  |  |  |

|                 |         | OTR      | None                                           |  |  |  |

|                 |         | STR      | None                                           |  |  |  |

|                 |         | MDR0     | None                                           |  |  |  |

| 4               | LOAD    | MDR1     | None                                           |  |  |  |

| 1               | LOAD    | DTR      | None                                           |  |  |  |

|                 |         | CNTR     | Transfer DTR to CNTR in "parallel"             |  |  |  |

|                 |         | OTR      | Transfer CNTR to OTR in "parallel"             |  |  |  |

|                 |         |          |                                                |  |  |  |

**MDR0.** The MDR0 (Mode Register 0) is an 8-bit read/write register that sets up the operating mode for the LS7366R. The MDR0 is written into by executing the "write-to-MDR0" instruction via the instruction register. Upon power up MDR0 is cleared to zero. The following is a breakdown of the MDR bits:

| B7 B6 B5 B4 B3 B2 B1 |

|----------------------|

|----------------------|

- B1 B0 = 00: non-quadrature count mode. (A = clock, B = direction).

- = 01: x1 quadrature count mode (one count per quadrature cycle).

- = 10: x2 quadrature count mode (two counts per quadrature cycle).

- = 11: x4 quadrature count mode (four counts per quadrature cycle).

- B3 B2 = 00: free-running count mode.

- = 01: single-cycle count mode (counter disabled with carry or borrow, re-enabled with reset or load).

- = 10: range-limit count mode (up and down count-ranges are limited between DTR and zero, respectively; counting freezes at these limits but resumes when direction reverses).

- = 11: modulo-n count mode (input count clock frequency is divided by a factor of (n+1), where n = DTR, in both up and down directions).

- B5 B4 = 00: disable index.

- = 01: configure index as the "load CNTR" input (transfers DTR to CNTR).

- = 10: configure index as the "reset CNTR" input (clears CNTR to 0).

- = 11: configure index as the "load OTR" input (transfers CNTR to OTR).

- B6 = 0: Asynchronous Index

- = 1: Synchronous Index (overridden in non-quadrature mode)

- B7 = 0: Filter clock division factor = 1

- = 1: Filter clock division factor = 2

**MDR1.** The MDR1 (Mode Register 1) is an 8-bit read/write register which is appended to MDR0 for additional modes. Upon power-up MDR1 is cleared to zero.

| B7 B6 | B5 | В4 | В3 | B2 | B1 | В0 |

|-------|----|----|----|----|----|----|

|-------|----|----|----|----|----|----|

- B1 B0 = 00: 4-byte counter mode

- = 01: 3-byte counter mode

- = 10: 2-byte counter mode.

- = 11: 1-byte counter mode

- B2 = 0: Enable counting

- = 1: Disable counting

- B3 = : not used

- B4 = 0: NOP

- = 1: FLAG on IDX (B4 of STR)

- B5 = 0: NOP

- = 1: FLAG on CMP (B5 of STR)

- B6 = 0: NOP

- = 1: FLAG on BW (B6 of STR)

- B7 = 0: NOP

- = 1: FLAG on CY (B7 of STR)

**NOTE:** Applicable to both LFLAG/ and DFLAG/

#### **ABSOLUTE MAXIMUM RATINGS:**

(All voltages referenced to Vss)

| Parameter             | Symbol | Values                 | Unit |

|-----------------------|--------|------------------------|------|

| DC Supply Voltage     | VDD    | +7.0                   | V    |

| Input Voltage         | VIN    | Vss - 0.3 to VDD + 0.3 | V    |

| Operating Temperature | TA     | -25 to +80             | oC   |

| Storage Temperature   | Tstg   | 65 to +150             | oC   |

| DC Electrical Characteristics.    | •      | ,            |      |      |      |                                                    |

|-----------------------------------|--------|--------------|------|------|------|----------------------------------------------------|

| Parameter                         | Symbol | Min.         | TYP  | Max. | Unit | Remarks                                            |

| Supply Voltage                    | VDD    | 3.0          | -    | 5.5  | V    | -                                                  |

| Supply Current                    | IDD    | 300          | 400  | 450  | μA   | VDD = 3.0V                                         |

|                                   | IDD    | 700          | 800  | 950  | μΑ   | VDD = 5.0V                                         |

| Input Voltages                    |        |              |      |      |      |                                                    |

| fcki, Logic high                  | VcH    | 2.3          | -    | -    | V    | VDD = 3.0V                                         |

|                                   | Vch    | 3.7          | -    | -    | V    | VDD = 5.0V                                         |

| fcki, Logic Low                   | VCL    | -            | -    | 0.7  | V    | VDD = 3.0V                                         |

|                                   | VCL    | -            | -    | 1.3  | V    | VDD = 5.0                                          |

| All other inputs, Logic High      | Vah    | 2.1          | -    |      | V    | VDD = 3.0V                                         |

|                                   | VAH    | 3.5          | -    |      | V    | VDD = 5.0V                                         |

| All other inputs, Logic Low       | VAL    | -            | -    | 0.5  | V    | VDD = 3.0V                                         |

|                                   | Val    | -            | -    | 1.0  | V    | VDD = 5.0V                                         |

| Input Currents:                   |        |              |      |      |      |                                                    |

| CNT_EN Low                        | liel   | -            | 3.0  | 5.0  | μA   | VAL = 0.7V, VDD = 3.0V                             |

| _                                 | liel   | -            | 10.0 | 15.0 | μA   | VAL = 1.2V, $VDD = 5.0V$                           |

| CNT_EN High                       | lieh   | _            | 1.0  | 3.0  | μA   | VAH = 1.9V, VDD = 3.0V                             |

|                                   | lieh   | _            | 4.0  | 6.0  | μA   | VAH = 3.2V, VDD = 5.0V                             |

| All other inputs, High or Low     | -      | _            | 0    | 0.0  | μA   | -                                                  |

| , in our or inpute, riight or zon |        |              | ·    |      | μ, , |                                                    |

| Output Currents:                  |        |              |      |      |      |                                                    |

| LFLAG, DFLAG Sink                 | IOFL   | -1.3         | -2.0 | -    | mA   | VOUT = 0.5V, VDD = 3.0V                            |

|                                   | IOFL   | -3.2         | -4.0 | -    | mA   | VOUT = 0.5V, $VDD = 5.0V$                          |

| LFLAG Source                      | -      | 0            | 0    | -    | mA   | Open Drain Output                                  |

| DFLAG Source                      | lоғн   | 1.0          | 1.8  | _    | mA   | $\dot{V}$ OUT = 2.5V, $\dot{V}$ DD = 3.0V          |

|                                   | IOFH   | 2.8          | 3.6  | -    | mA   | VOUT = 4.5V, $VDD = 5.0V$                          |

| fcко Sink                         | locl   | -1.3         | -2.0 | _    | mA   | VOUT = 0.5V, VDD = 3.0V                            |

|                                   | locu   | -3.2         | -4.0 | _    | mA   | VOUT = 0.5V, VDD = 5.0V                            |

| fcko Source                       | Іосн   | 1.3          | 2.0  | _    | mA   | VOUT = 2.5V, VDD = 3.0V                            |

|                                   | Іосн   | 3.2          | 4.0  | _    | mA   | VOUT = 4.5V, VDD = 5.0V                            |

| TXD/MISO:                         |        | <del>-</del> |      |      |      | 111, 122 0101                                      |

| Sink                              | IOML   | -1.5         | -2.4 |      | mA   | VOUT = 0.5V, VDD = 3.0V                            |

|                                   | IOML   | -3.8         | -4.8 |      | mA   | VOUT = 0.5V, VDD = 5.0V                            |

| Source                            | Іомн   | 1.5          | 2.4  |      | mA   | VOUT = 2.5V, VDD = 3.0V                            |

| Source                            | IOMH   | 3.8          | 4.8  | -    | mA   | VOUT = 2.5V, VDD = 3.0V<br>VOUT = 4.5V, VDD = 5.0V |

Transient Characteristics. (TA =  $-25^{\circ}$ C to  $+85^{\circ}$ C, VDD = 5V ± 10%)

| Parameter                            | Symbol   | Min. Value | Max.Value   | Unit | Remarks                            |

|--------------------------------------|----------|------------|-------------|------|------------------------------------|

| (See Fig. 2)                         | ,        |            |             |      |                                    |

| SCK High Pulse Width                 | tch      | 100        | -           | ns   | -                                  |

| SCK Low Pulse Width                  | tCL      | 100        | -           | ns   | -                                  |

| SS/ Set Up Time                      | tcsL     | 100        | -           | ns   | -                                  |

| SS/ Hold Time                        | tcsh     | 100        | -           | ns   | -                                  |

|                                      |          |            |             |      |                                    |

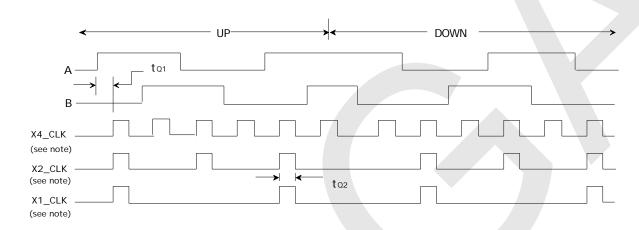

| Quadrature Mode                      |          |            |             |      |                                    |

| (See Fig. 5, 7 & 8)                  |          |            |             |      |                                    |

| fcki High Pulse Width                | t1       | 12         | -           | ns   | -                                  |

| fcki Pulse Width                     | t2       | 12         | -           | ns   | -                                  |

| fcki Frequency                       | fFCK     | -          | 40          | MHz  | -                                  |

| Effective Filter Clock fr Period     | t3       | 25         | -           | ns   | $t_3 = t_1 + t_2$ , MDR0 <7> = 0   |

|                                      | t3       | 50         | -           | ns   | $t_3 = 2(t_1+t_2), MDR0 < 7 > = 1$ |

| Effective Filter Clock fr frequency  | fF       | -          | 40          | MHz  | fF = 1/t3                          |

| Quadrature Separation                | t4       | 26         | -           | ns   | t4 > t3                            |

| Quadrature Clock Pulse Width         | t5       | 52         | -           | ns   | t5 2t3                             |

| Quadrature Clock frequency           | fqa, fqb | -          | 9.6         | MHz  | fQA = fQB < 1/4t3                  |

| Quadrature Clock to Count Delay      | tQ1      | 4t3        | <b>5t</b> 3 | -    | -                                  |

| x1 / x2 / x4 Count Clock Pulse Width | tQ2      | 12         | -           | ns   | tQ2 = (t3)/2                       |

| Index Input Pulse Width              | tid      | 32         | -           | ns   | tid > t4                           |

| Index Set Up Time                    | tis      | -          | 5           | ns   | -                                  |

| Index Hold Time                      | tih      | -          | 5           | ns   | -                                  |

| Quadrature clock to                  | tfl      | 4.5t3      | 5.5t3       | ns   | -                                  |

| DFLAG/ or LFLAG/ delay               |          |            |             |      |                                    |

| DFLAG/ output width                  | tfw      | 26         | -           | ns   | $t_{fw} = t_4$                     |

|                                      |          |            |             |      |                                    |

| Parameter<br>Non-Quadrature Mode   | Symbol      | Min. Value | Max.Value | Unit | Remarks            |

|------------------------------------|-------------|------------|-----------|------|--------------------|

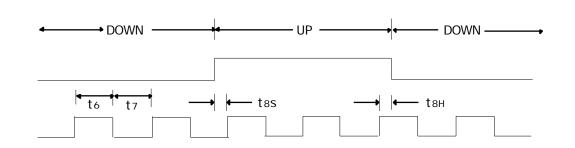

| (See Fig. 6 & 9)                   |             |            |           |      |                    |

| Clock A - High Pulse Width         | t6          | 12         | -         | ns   | -                  |

| Clock A - Low Pulse Width          | t7          | 12         | -         | ns   | -                  |

| Direction Input B Set-up Time      | t8S         | 12         | -         | ns   | -                  |

| Direction Input B Hold Time        | t8H         | 10         | -         | ns   | -                  |

| Clock Frequency (non-Mod-N)        | fA          | -          | 40        | MHz  | fA = (1/(t6 + t7)) |

| Clock to DFLAG/ or<br>LFLAG/ delay | t9          | 20         | -         | ns   |                    |

| DFLAG/ output width                | <b>t</b> 10 | 12         | -         | ns   | t10 = t7           |

Transient Characteristics. (TA = -25 $^{\circ}$ C to +85 $^{\circ}$ C, VDD = 3.3V ± 10%)

| Parameter                                                 | Symbol               | Min. Value            | Max.Value   | Unit      | Remarks                            |

|-----------------------------------------------------------|----------------------|-----------------------|-------------|-----------|------------------------------------|

| (See Fig. 2)                                              | -                    |                       |             |           |                                    |

| SCK High Pulse Width                                      | tch                  | 120                   | -           | ns        | -                                  |

| SCK Low Pulse Width                                       | tCL                  | 120                   | -           | ns        | -                                  |

| SS/ Set Up Time                                           | tCSL                 | 120                   | -           | ns        | -                                  |

| SS/ Hold Time                                             | tcsh                 | 120                   | -           | ns        | - 1                                |

|                                                           |                      |                       |             |           |                                    |

| Quadrature Mode                                           |                      |                       |             |           |                                    |

| (See Fig. 5, 7 & 8)                                       |                      |                       |             |           |                                    |

| fcкı High Pulse Width                                     | t1                   | 24                    | -           | ns        | -                                  |

| fcki Pulse Width                                          | t2                   | 24                    | -           | ns        | -                                  |

| fcki Frequency                                            | fFCK                 | -                     | 20          | MHz       | -                                  |

| Effective Filter Clock fF Period                          | t3                   | 50                    | -           | ns        | $t_3 = t_1 + t_2$ , MDR0 <7> = 0   |

|                                                           | t3                   | 100                   | -           | ns        | $t_3 = 2(t_1+t_2), MDR0 < 7 > = 1$ |

| Effective Filter Clock fr frequency                       | fF                   | -                     | 20          | MHz       | fF = 1/t3                          |

| Quadrature Separation                                     | t4                   | 52                    | -           | ns        | t4 > t3                            |

| Quadrature Clock Pulse Width                              | <b>t</b> 5           | 105                   | -           | ns        | t5 2t3                             |

| Quadrature Clock frequency                                | fQA, fQB             | -                     | 4.5         | MHz       | fQA = fQB < 1/4t3                  |

| Quadrature Clock to Count Delay                           | tQ1                  | 4t3                   | <b>5t</b> 3 | -         | -                                  |

| x1/x2/x4 Count Clock Pulse Width                          | tQ2                  | 25                    | -           | ns        | tQ2 = (t3)/2                       |

| Index Input Pulse Width                                   | tid                  | 60                    | -           | ns        | tid > t4                           |

| Index Set Up Time                                         | tis                  | -                     | 10          | ns        | -                                  |

| Index Hold Time                                           | tih                  | ·                     | 10          | ns        | -                                  |

| Quadrature clock to                                       | tfl                  | 4.5t3                 | 5.5t3       | ns        | -                                  |

| DFLAG/ or LFLAG/ delay                                    |                      |                       |             |           |                                    |

| DFLAG/ output width                                       | tfw                  | 52                    | -           | ns        | $t_{fw} = t_4$                     |

|                                                           |                      |                       |             |           |                                    |

| Non-Quadrature Mode                                       |                      |                       |             |           |                                    |

|                                                           |                      |                       |             |           |                                    |

| (See Fig. 6 & 9)<br>Clock A - High Pulse Width            | t <sub>6</sub>       | 24                    |             | ns        |                                    |

| Clock A - Fight Fulse Width                               | ι <sub>ο</sub><br>t7 | 2 <del>4</del><br>24  | -           | _         | -                                  |

| Direction Input B Set-up Time                             | t8S                  | 24<br>24              | -           | ns        | -                                  |

| Direction Input B Set-up Time Direction Input B Hold Time |                      | 2 <del>4</del><br>24  | -           | ns        | -                                  |

|                                                           | t8H<br>fA            | 2 <del>4</del>        | -<br>40     | ns<br>MHz | fA = (1/(t6 + t7))                 |

| Clock Frequency (non-Mod-N) Clock to DFLAG/or             | t9                   | -<br>40               | 40          |           | IA = (I/(to + t/))                 |

| LFLAG/ delay                                              | 19                   | 40                    | -           | ns        | -                                  |

| DFLAG/ output width                                       | <b>t</b> 10          | 24                    | _           | ns        | t10 = t7                           |

| DI LAG/ Output width                                      | LIU                  | <b>∠</b> <del>1</del> | -           | 110       | 110 – 17                           |

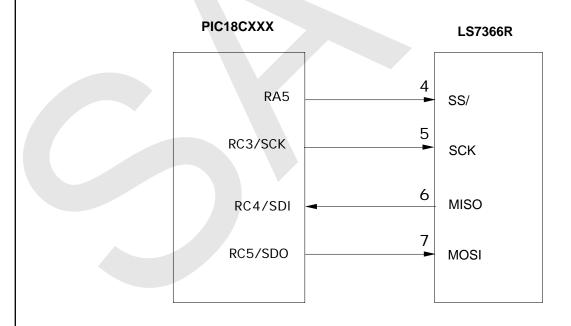

Note 1. The SPI port of the host MCU must be set up as follows:

- 1. SPI master mode.

- 2. SCK idle state = low

- 3. Clock edge for MOSI data shift = high to low

4. Clock edge for input data (MISO) sample by the Processor = low to high (or bit middle)

**Note 2.** To conform with the multibyte transmission protocol of LS7366R, the SS/ output port of the MCU may require direct manipulation by the application program.

FIGURE 2. SPI TIMINGS

tcsi SS/ sck CLR- STR Х Х RANDOM DATA X x x MOSI 3 2 1 BYTE 1 BYTE 0-MISO D6 D5 D4 D3 D2 D1 D0 BIT # TRI-STATE

NOTE: Read CNTR (in 2-byte configuration) followed by CLR STR operation.

FIGURE 4. RD CNTR - CLR STR

- Note 1. Synchronous index coincident with both A and B high.

- Note 2. Synchronous index coincident with both A and B low..

- Note 3. fF is the internal effective filter clock.

# FIGURE 5. fcki, A, B and INDEX

FIGURE 6. COUNT (A) AND DIRECTION (B) INPUTS IN NON-QUADRATURE MODE

Note: x1, x2, and x4 CLKs are internal up/down clocks derived from filtered and decoded quadrature clocks.

FIGURE 7. A/B QUADRATURE CLOCKS vs INTERNAL COUNT CLOCKS

Note: CNTR values are indicated in 3-byte mode

FIGURE 8. QUADRATURE CLOCKS vs FLAG OUTPUTS

FIGURE 13. GENERAL I/O CONNECTIONS

FIGURE 14. PIC18C TO LS7366R

# ;Sample routines for PIC18CXXX interface

- ;Initialize PIC18Cxxx portc in LS7366 compatible SPI

- ;Setup: master mode, SCK idle low, SDI/SDO datashift on high to low transition of SCK

- ;SS/ assertion/deassertion made with direct manipulation of RA5

### ;Initialize portc

| CLRF  | PORTC   | ;Clear portc                         |

|-------|---------|--------------------------------------|

| CLRF  | LATC    | ;Clear data latches                  |

| MOVLW | 0x10    | ;RC4 is input, RC3 & RC5 are outputs |

| MOVWF | TRISC   | ;RC3=CLK, RC4=SDI, RC5=SDO           |

| DCE   | TDICA E | ·DAF—output                          |

;RA5=output BCF TRISA, 5 BSF ;RA5=SS/=high PORTA, 5

CLRF SSPSTAT ;SMP=0 => SDI data sampled at mid-data

BSF SSPSTAT, CKE ;CKE=1 => data shifts on active to idle SCK transitions

;SPI mode initialization data MOVLW 0x21

MOVWF **SSPCON** ;Master mode, CLK/16, CKP=0 => CLK idles low

;data shifted on active to idle CLK edge

# ; WR\_MDR0

```

BSF

PORTA, 5

:SS/=high

BCF

PORTA, 5

;SS/=low

MOVLW

;LS7366 WR MDR0 command

0x88

MOVWF

SSPBUF

Transmit command byte

LOOP1 BTFSS

;Transmission complete with BF flag set?

SSPSTAT, BF

BRA

LOOP1

;No, check again

MOVF

SSPBUF, W

;Dummy read to clear BF flag.

MOVLW

0xA3

;MDR0 data:fck/2, synchronous index. index=rcntr, x4

:Transmit data

MOVWF

SSPBUF

:BF set?

LOOP2 BTFSS

SSPSTAT, BF

;No, check again

BRA

LOOP2

BSF

PORTA, 5

;SS/=high

```

# ;RD\_MDR0

|       | BSF   | PORTA, 5    | ;SS/=high                                         |

|-------|-------|-------------|---------------------------------------------------|

|       | BCF   | PORTA, 5    | ;SS/=low                                          |

|       | MOVLW | 0x48        | ;LS7366 RD_MDR0 command                           |

|       | MOVWF | SSPBUF      | ;Transmit command byte                            |

| LOOP1 | BTFSS | SSPSTAT, BF | ;BF flag set?                                     |

|       | BRA   | LOOP1       | ;No, check again                                  |

|       | MOVWF | SSPBUF      | ;Send dummy byte to generate clock & receive data |

| LOOP2 | BTFSS | SSPSTAT, BF | ;BF flag set?                                     |

|       | BRA   | LOOP2       | ;No, check again                                  |

|       | MOVF  | SSPBUF, W   | ;Recieved data in WREG.                           |

|       | MOVWF | RXDATA      | ;Save received data in RAM                        |

|       | BSF   | PORTA, 5    | :SS/=high                                         |